- 您现在的位置:买卖IC网 > Sheet目录344 > MPC8272ADS (Freescale Semiconductor)KIT DEVELOPMENT MPC8272

�� �

�

Interconnect� Signals�

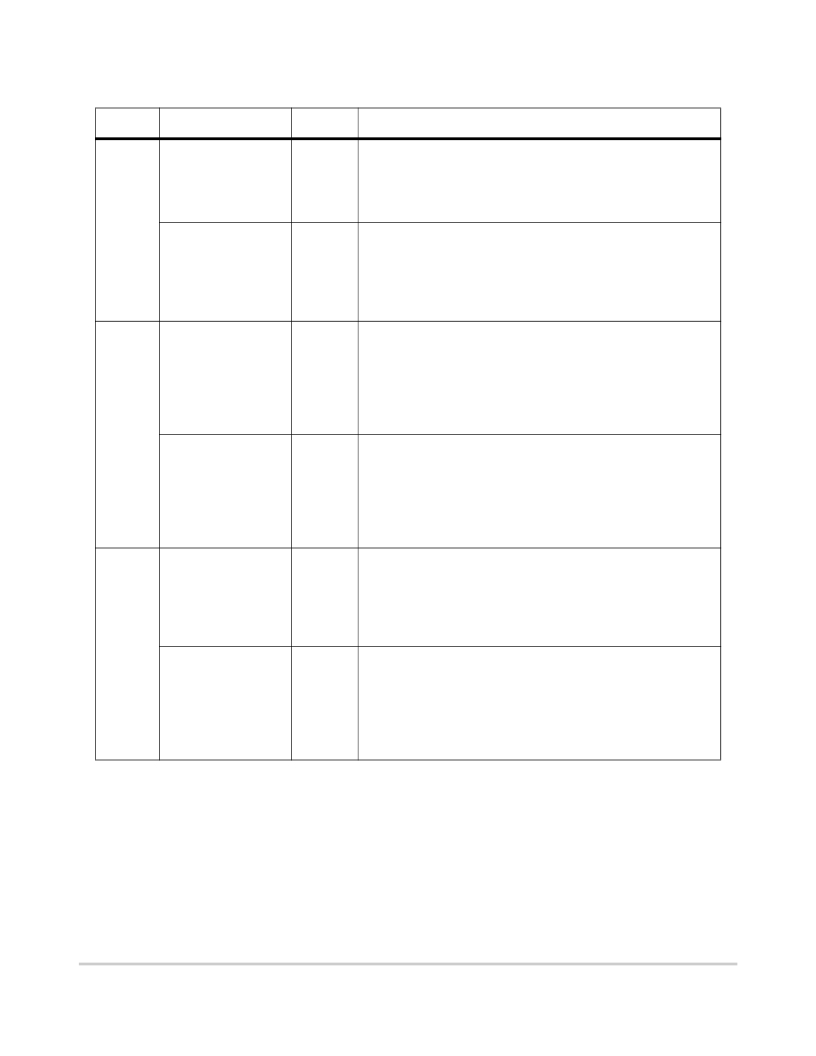

�Table� 8-4.� P1—CPM� Expansion� Connector� (continued)�

�Pin� No.�

�B1�

�Signal� Name�

�ATMTXEN#� (PA31)�

�Attribute�

�I/O,� T.S.�

�Description�

�ATM� Transmit� Enabled� (L).� When� this� signal� is� asserted� (Low),�

�while� the� ATM� port� is� enabled� and� ATMTFCLK� is� rising,� an� octet� of�

�data,� ATMTXD(7:0),� is� written� into� the� transmit� FIFO� of� the�

�PM5384.� When� the� ATM� port� is� disabled,� this� line� may� be� used� for�

�any� available� function� of� PA31.�

�FETH1COL� (PA31)�

�I/O,� T.S.�

�Fast-Ethernet� Port� 1� Collision� Detected� (H).� When� this� signal� is�

�asserted� (High)� by� the� DM9161,� while� the� ethernet� port� is� enabled,�

�it� indicates� a� Collision� state� over� the� line.� When� the� DM9161� is� in�

�Full-Duplex� mode,� this� line� is� inactive.�

�When� the� Ethernet� port� is� disabled,� this� line� is� tristated� and� may� be�

�used� for� any� available� function� of� the� PA31.�

�B2�

�ATMTCA� (PA30)�

�I/O,� T.S.�

�ATM� Transmit� Cell� Available� (H).� When� this� signal� is� asserted�

�(High),� while� the� ATM� port� is� enabled,� it� indicates� that� the� transmit�

�FIFO� of� the� PM5384� is� empty� and� ready� to� except� a� new� cell.�

�When� negated,� it� may� show� either� that� the� transmit� FIFO� is� Full� or�

�close� to� Full,� depending� on� PM5384� internal� programming.�

�When� the� ATM� port� is� disabled,� this� line� may� be� used� for� any�

�available� function� of� PA30.�

�FETH1CRS� (PA30)�

�I/O,� T.S.�

�Fast-Ethernet� 1� Carrier� Sense� (H).� When� this� signal� is� asserted�

�(High),� while� the� Ethernet� port� is� enabled� and� the� DM9161� is� in�

�half-duplex� mode,� it� indicates� that� either� the� transmit� or� receive�

�media� are� non-idle.� When� the� DM9161� is� in� either� full-duplex� or�

�repeater� operation,� it� indicates� that� the� receive� medium� is� non-idle.�

�When� the� Ethernet� port� is� disabled,� this� line� may� be� used� for� any�

�available� function� of� PA30.�

�B3�

�ATMTSOC� (PA29)�

�I/O,� T.S.�

�ATM� Transmit� Start� Of� Cell� (H).� When� this� signal� is� asserted� (High)�

�by� the� PowerQUICC� II,� while� the� ATM� port� is� enabled,� it� indicates�

�to� the� PM5384� the� start� of� a� new� ATM� cell� over� ATMTXD(7:0),� i.e.,�

�the� 1’st� octet� is� present� there.�

�When� the� ATM� port� is� disabled,� this� line� may� be� used� for� any�

�available� function� of� PA29.�

�FETH1TXER� (PA29)�

�I/O,� T.S.�

�Fast-Ethernet� 2� 1� Transmit� Error� (H).� When� the� Ethernet� port� is�

�enabled,� this� signal� will� be� asserted� (High)� by� the� PowerQUICC� II�

�when� an� error� is� discovered� in� the� transmit� data� stream.� When� the�

�port� is� operation� at� 100� Mbps,� the� DM9161� responds� by� sending�

�invalid� code� symbols� on� the� line.�

�When� the� Ethernet� port� is� disabled,� this� line� may� be� used� for� any�

�available� function� of� PA29.�

�MPC8272ADS� User� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MPC8308-RDB

BOARD REF DESIGN MPC8308

MPC8309-KIT

KIT EVALUATION FOR MPC830X

MPC8315E-RDB

PROCESSOR BOARD PWRQUICCII PBGA

MPC8349E-MITX-GP

KIT REFERENCE PLATFORM MPC8349E

MPC8349E-MITXE

BOARD REFERENCE FOR MPC8349

MPC8377E-MDS-PB

BOARD MODULAR DEV SYSTEM

MPC8569E-MDS-PB

BOARD MOD DEV SYSTEM MPC8569

MPC8572EAMC

MPC8572 AMC RAPID SYSTEM

相关代理商/技术参数

MPC8272CVR

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:MPC8272 PowerQUICC II Family Hardware Specifications

MPC8272CVRB

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications

MPC8272CVRE

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications

MPC8272CVRI

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications

MPC8272CVRM

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications

MPC8272CVRMIBA

功能描述:微处理器 - MPU 266 MHz 505.4 MIPS

RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324

MPC8272CVRP

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications

MPC8272CVRPIEA

功能描述:微处理器 - MPU 300 MHz 570 MIPS

RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324